# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Fast machine translation on parallel and massively parallel hardware

Nikolay Bogoychev

Doctor of Philosophy

Institute for Language, Cognition and Computation

School of Informatics

University of Edinburgh

2019

### **Abstract**

Parallel systems have been widely adopted in the field of machine translation, because the raw computational power they offer is well suited to this computationally intensive task. However programming for parallel hardware is not trivial as it requires redesign of the existing algorithms. In my thesis I design efficient algorithms for machine translation on parallel hardware. I identify memory accesses as the biggest bottleneck to processing speed and propose novel algorithms that minimize them. I present three distinct case studies in which minimizing memory access substantially improves speed: Starting with statistical machine translation, I design a phrase table that makes decoding ten times faster on a multi-threaded CPU. Next, I design a GPU-based *n*-gram language model that is twice as fast per £ as a highly optimized CPU implementation. Turning to neural machine translation, I design new stochastic gradient descent techniques that make end-to-end training twice as fast. The work in this thesis has been incorporated in two popular machine translation toolkits: Moses and Marian.

## **Lay Summary**

Machine translation systems, such as Google translate and Microsoft translator, Baidu fanyi, etc, have become increasingly more popular in the recent years. Machines translate more than one billion words daily, however producing said translations is quite computationally expensive and requires hundreds of millions of computer chips working around the clock. In my thesis, I explain why machine translation systems require so much computational power. I also carefully examine the characteristics of modern computer chips and note that often the speed of memory is the limiting factor for achieving faster performance. I use that knowledge to design algorithms that can make machine translation much more efficient on modern hardware, increasing translation speed up to ten fold compared to previous state of the art work.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

May 17, 2019

(Nikolay Bogoychev)

## **Acknowledgements**

PhD has been long journey filled with unexpected twists. My field changed completely in my first year of study, I ended up living in a few different countries, experienced multiple highs and lows met a many wonderful people, learned a fair bit of new things and grew up into a better person... I struggled for many sleepless nights, wondering whether I would finish this at all. Fortunately I got plenty of emotional support from my supervisors and my peers and above all I understood that a PhD is about learning, perseverance and continuous self improvement. Every rejection, however painful, should also a motivation to do better in the future. I did not learn that by myself, but with ample help from supervisors, coworkers and friends I accepted it. I want to thank my precious office mates, past and present: Joana, Federico, Maria, Mihaela, Vanya, Jason (whose name I kept forgetting), Sefa, Esma, Chao, Aurora, Andrew, Ratish for all the laughter, support and motivation they brought me. I want to thank coworkers around the forum: Carol, Craig, Clara, Ida, John, Matt, Naomi, Pippa, Sabine, Sander, Sameer, Sorcha, Stefanie, Toms for the nice time, the feedback on papers and bitching about other people. I want to thank the machine translation group for giving me this wonderful opportunity to do a PhD in the first place and helping me grow as a researcher. Thank you Barry, Uli, Rachel, Dominikus, Bonnie, Jozef, Marcin, Sonya, Ana, Maxi, Alham, Christian, Phil, Rico, Faheem, Roman. I thank Hieu for taking me as a student during my undergraduate and helping me with my first steps in C++. I thank Kenneth for the discussions and guidance on high performance optimization, as well as for the countless friendly conversations we've had as I dropped by your office. I give very special thanks to Adam for taking me as a student when he knew so little about me, for his patience with my continuous refusal to learn tikz (or math), for supporting me emotionally and encouraging me through my lows, for insisting that I learn to read and write and understand papers well and for always asking the question: "What does this tell us?" (And the ever present "Can you draw a figure of that (using tikz preferably)?"). I thank Lexi for being a friend to me, for the countless times we've gone for a coffee and laughter and for teaching me how to navigate the complex academic world. I thank Stefan, Ivo, Rumi, Jenny, Esther, Yves, Schuyler (male), Schuyler (female), Vyara, good friends and treasured flatmates, with whom we have shared laughs, home cooked food and woes over all my years in Edinburgh, California and Berlin. I thank Marto, George, Svetla, Irina, Sparkz, Boiko, Nasco, Nicky, Dani, Bats for the many hours online spent playing Dota, for the awesome time in real life, for the seaside holidays, for the friendship that has endured since high school and for the support they have offered to me in one form or another over the past decade. I thank Tanya for the years of friendship and for putting up with me at my low points and for encouraging me to push through the difficulties. I thank Nevelina for more than a decade of putting up with me and for always being there for me. I thank Katya, Nadya, Pamela, Steve, Iana, Maya, Pei for the ever present support-network-from-the-other-side-of-the-world they offered. I thank Lousi for helping me grow as a person, face my problems and encouraging me to work on them, as well as the emotional support and fun times we've had together. Finally I want to thank my family Vesco, Valia, Marti and my grandparents Toshko, Mari, Kolyo, Kalinka for providing me with the opportunity to study abroad, for their unconditional support 24 hours a day and for putting up with me when I was being the most difficult.

#### **Grants**

The work in Chapters 3 and 4 conducted within the scope of the Horizon 2020 Innovation Action *Modern MT*, which has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 645487.

The work in Chapter 3 sponsored by the Air Force Research Laboratory, prime contract FA8650-11-C-6160. The views and conclusions contained in this document are those of the authors and should not be interpreted as representative of the official policies, either expressed or implied, of the Air Force Research Laboratory or the U.S. Government.

For the work in Chapter 5, Nikolay Bogoychev was funded by an Amazon faculty research award to Adam Lopez.

We thank Adam Lopez, Kenneth Heafield, Ulrich Germann, Rico Sennrich, Hieu Hoang, Federico Fancellu, Nathan Schneider, Naomi Saphra, Sorcha Gilroy, Clara Vania, Marcin Junczys-Dowmunt, Sameer Bansal, Lexi Birch and the anonymous reviewers for productive discussion for the work involved in chapters 3, 4 and 5 and helpful comments on previous drafts of the related papers. Any errors are my own.

## **Table of Contents**

| 1 | Intr | oductio   | n                                                           | 13 |

|---|------|-----------|-------------------------------------------------------------|----|

|   | 1.1  | Thesis    | structure                                                   | 17 |

|   | 1.2  | Contri    | butions                                                     | 18 |

| 2 | Para | allel pro | ogramming and Machine Translation                           | 19 |

|   | 2.1  | Paralle   | el hardware                                                 | 20 |

|   |      | 2.1.1     | On a single chip                                            | 20 |

|   |      | 2.1.2     | On a single Machine                                         | 22 |

|   |      | 2.1.3     | On a single network                                         | 22 |

|   | 2.2  | Why p     | arallel programming is hard                                 | 22 |

|   |      | 2.2.1     | Memory                                                      | 25 |

|   | 2.3  | Machi     | ne Translation                                              | 27 |

|   |      | 2.3.1     | Statistical Machine Translation                             | 27 |

|   |      | 2.3.2     | Neural Machine translation                                  | 31 |

|   | 2.4  | Conclu    | asion                                                       | 32 |

| 3 | Phra | ase tabl  | e for for symmetric multiprocessors                         | 33 |

|   | 3.1  | Proble    | ms with current implementations                             | 35 |

|   | 3.2  | Probin    | gPT                                                         | 36 |

|   |      | 3.2.1     | Integrated lexical reordering                               | 38 |

|   | 3.3  | Experi    | mental setup                                                | 39 |

|   |      | 3.3.1     | Decoders                                                    | 39 |

|   |      | 3.3.2     | PhraseTables                                                | 40 |

|   | 3.4  | Result    | s                                                           | 40 |

|   |      | 3.4.1     | Why is CompactPT slower?                                    | 42 |

|   |      | 3.4.2     | Order of magnitude performance improvements with integrated |    |

|   |      |           | reordering table                                            | 43 |

|   | 3.5  | Evalua   | ation                                                     | 44 |

|---|------|----------|-----------------------------------------------------------|----|

|   |      | 3.5.1    | Profiling the code                                        | 44 |

|   | 3.6  | Conclu   | asion                                                     | 45 |

| 4 | N-gı | ram lan  | guage models for massively parallel devices               | 47 |

|   | 4.1  | GPU c    | computational model                                       | 48 |

|   |      | 4.1.1    | GPU design                                                | 48 |

|   |      | 4.1.2    | Designing efficient GPU algorithms                        | 50 |

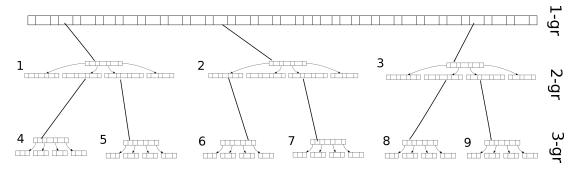

|   | 4.2  | A mas    | sively parallel language model                            | 51 |

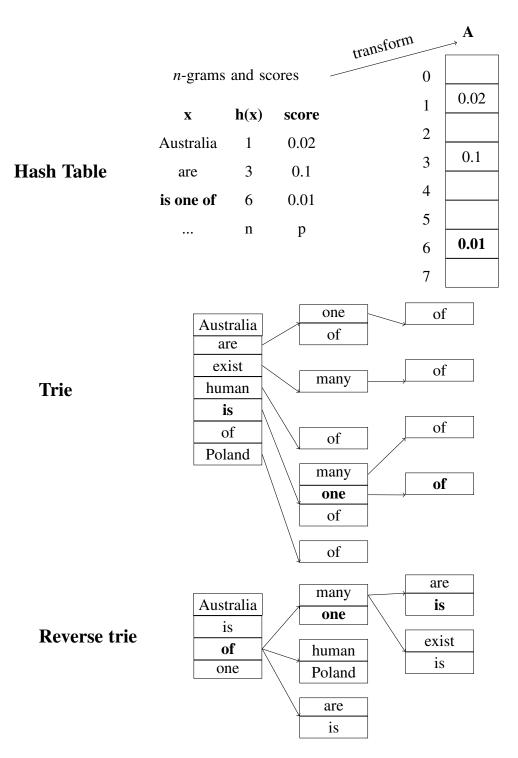

|   |      | 4.2.1    | Language model data structures                            | 52 |

|   | 4.3  | Data s   | tructures used in my implementation                       | 55 |

|   |      | 4.3.1    | Reverse trie                                              | 55 |

|   |      | 4.3.2    | <i>K</i> -ary search                                      | 56 |

|   |      | 4.3.3    | B-tree                                                    | 57 |

|   | 4.4  | Memo     | ry layout and implementation                              | 58 |

|   |      | 4.4.1    | Constructing minimum depth B-trees                        | 60 |

|   |      | 4.4.2    | Batch queries                                             | 60 |

|   | 4.5  | Experi   | ments                                                     | 60 |

|   |      | 4.5.1    | Query speed                                               | 61 |

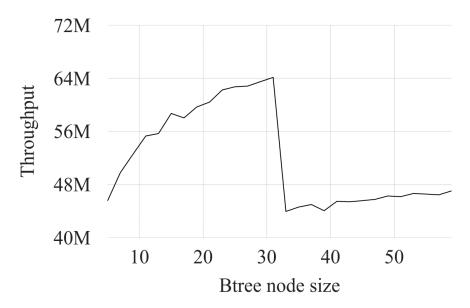

|   |      | 4.5.2    | Effect of B-tree node size                                | 62 |

|   |      | 4.5.3    | Saturating the GPU                                        | 63 |

|   |      | 4.5.4    | Effect of model size                                      | 64 |

|   |      | 4.5.5    | Effect of <i>N</i> -gram order on performance             | 64 |

|   |      | 4.5.6    | Bottlenecks: computation or memory?                       | 65 |

|   | 4.6  | Conclu   | usion and Future work                                     | 66 |

| 5 | Acce | eleratin | g Asynchronous Stochastic Gradient Descent on distributed | i  |

|   |      | lware    | C v                                                       | 67 |

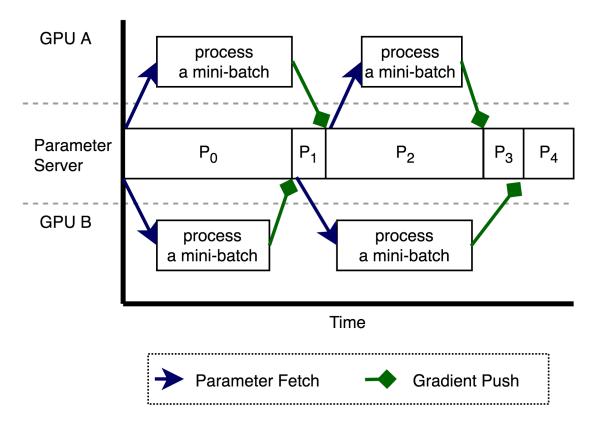

|   | 5.1  | Paralle  | el asynchronous SGD                                       | 72 |

|   | 5.2  |          | sing performance with larger batches and delayed updates  | 73 |

|   |      | 5.2.1    | Evaluation metrics                                        | 73 |

|   |      | 5.2.2    | Baseline systems                                          | 74 |

|   |      | 5.2.3    | Large mini-batches and delayed gradient updates           | 75 |

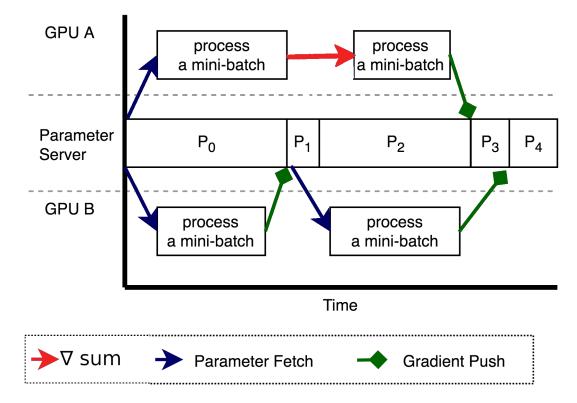

|   | 5.3  |          | ving model convergence                                    | 78 |

|   |      | 5.3.1    | Warmup                                                    | 78 |

|   |      | 5.3.2    | Momentum tuning and momentum cooldown                     | 80 |

| 1 | 1 |  |

|---|---|--|

| • | • |  |

| Ril | hlingr | anhv    |                               | 99 |

|-----|--------|---------|-------------------------------|----|

| A   | Cycl   | ical wa | rmup and random learning rate | 97 |

| 6   | Cone   | clusion |                               | 93 |

|     | 5.8    | Conclu  | sion and Future work          | 91 |

|     | 5.7    | Related | d work                        | 90 |

|     |        | 5.6.2   | Cyclic learning rate          | 89 |

|     |        | 5.6.1   | Flexible learning rate        | 88 |

|     | 5.6    | Further | explorations                  | 88 |

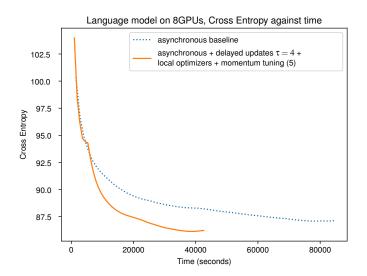

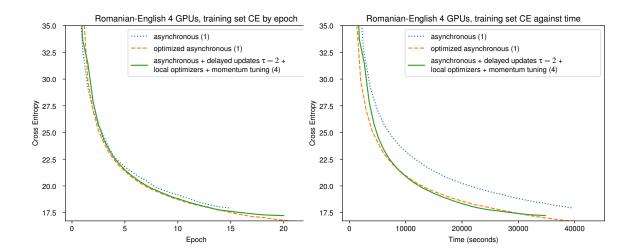

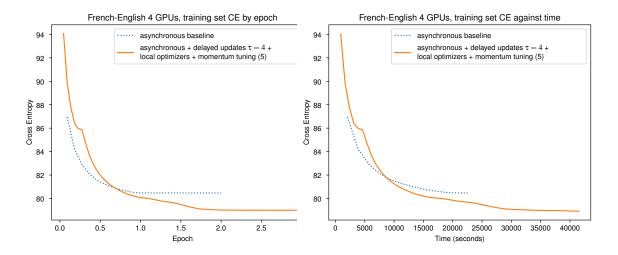

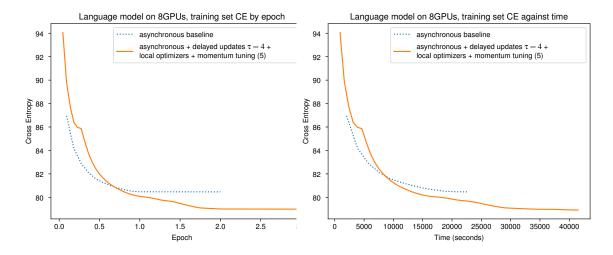

|     | 5.5    | Trainin | ng set Cross Entropy          | 86 |

|     |        | 5.4.3   | A language model              | 85 |

|     |        | 5.4.2   | A high resource language pair | 85 |

|     |        | 5.4.1   | A deep RNN                    | 83 |

|     | 5.4    | Additio | onal applications             | 83 |

|     |        | 5.3.3   | Results summary               | 82 |

## **Chapter 1**

## Introduction

Every day, Twitter users write 500 million tweets, Facebook users produce 734 million comments, and Google news serves stories from more than 50 thousand news agencies. 12345 Three billion people can access this text, but they can each understand only a small fraction of the knowledge it contains, because most of it is in one of the thousands of languages they don't speak. In order to make the world's knowledge accessible to everyone, it must be translated into everyone's language. To do so, translation must be automated, and the demand for this automation is clear: Google translate serves more than 200 million people a day, processing more text than all the world's human translators process in a year. The scale of machine translation requires immense computational cost, hence financial cost. Cost also limits the speed of machine translation research, where the goal is to improve the quality of next generation systems. To produce a single experiment, a machine translation researcher must first train a system, which requires translating more than 1 billion sentences using a neural network.<sup>7</sup> To compare two systems, this process must be repeated twice. To compare two systems on five languages — ten times. To truly improve the quality may take hundreds of such experiments. The high computational cost of machine translation leads to low throughput and is a bottleneck to improving its quality as well as availability.

Conveniently, advancements in computer hardware have kept up with the everincreasing amount of data available. However the nature of these advancements has

<sup>&</sup>lt;sup>1</sup>http://www.internetlivestats.com/twitter-statistics/

<sup>&</sup>lt;sup>2</sup>https://www.dsayce.com/social-media/tweets-day/

<sup>&</sup>lt;sup>3</sup>https://www.quora.com/How-many-Facebook-posts-are-shared-every-day

<sup>&</sup>lt;sup>4</sup>http://thesocialskinny.com/tag/social-media-statistics/

<sup>&</sup>lt;sup>5</sup>https://www.theguardian.com/technology/2013/feb/25/1

<sup>&</sup>lt;sup>6</sup>http://www.cnet.com/news/google-translate-now-serves-200-million-people-daily/

<sup>&</sup>lt;sup>7</sup>For example, Google (Wu et al., 2016) reported that training their system takes 1 week on 8 GPUs.

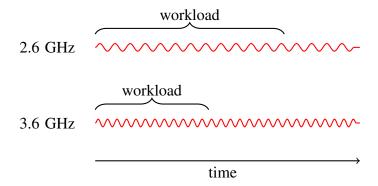

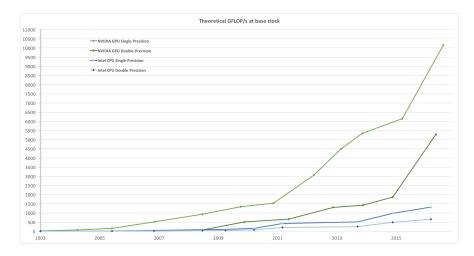

changed. More than a decade ago the application's performance would improve by upgrading the CPU to a newer one due to increased clock frequency (Figure 1.1).

**Figure 1.1:** Speed improvement with CPU generation upgrades. Each tick-tock (spike) on the graph represents a clock cycle.

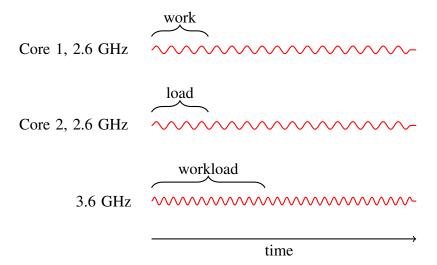

New generation hardware fundamentally differs from older generations, because it is highly parallel, with several slower cores per chip instead of one faster one (Figure 1.2). This allows for higher theoretical performance, but only if the application is parallelizeable, which is not always the case. In contrast, a faster clocked CPU would universally yield increased performance regardless of the application design.

**Figure 1.2:** Splitting the *workload* in two even parts *work* and *load* over two CPUs results in less wall-clock time necessary for completion of the task, even if the individual CPUs are slower.

In 2010, consumer-grade CPUs had four cores for top-of-the line models, with manufacturers focusing mostly on dual-core high clock solutions. Professional grade CPUs were manufactured with up to eight cores. General purpose graphics processing units (GPGPUs) were just being rolled out, with only a few proof-of-concept applications being written. Mobile phones used slow single core processors. In 2018,

Intel's latest generation of consumer grade hardware offers at least 4 cores and up to 18 cores. AMD's latest generation of consumer grade hardware has gone even more parallel, starting from 6 cores per chip, and up to 32. Mobile hardware is no different, with latest Apple and Android devices featuring dual-cluster multi-core solutions with one high performance multi-core CPU and one power efficient multi-core CPU.<sup>8</sup> In the GPU world the trends are similar with every consecutive generation having more streaming multiprocessors and more cores: From 15 and 2,880 in 2014<sup>9</sup> to 80 and 5,120 in 2018.<sup>10</sup> The trends is to go towards higher core count, rather than faster clock frequency due thermal and physical limits in the CPU design.

Hardware has changed dramatically over the past 8 years, but software has not changed much over the same timeframe. Machine translation toolkits are seldom optimized for parallel hardware because this is a difficult task. Most algorithms are inherently sequential in nature, and as such it is difficult to extract computational parts that can run concurrently (Perrone, 2009). In order for any application to scale (or to even be compatible) with future hardware, it must be redesigned with parallelism in mind (Figure 1.2) and also with the idea that parallelism in the future is likely to increase, while single-core performance is not likely to increase much.

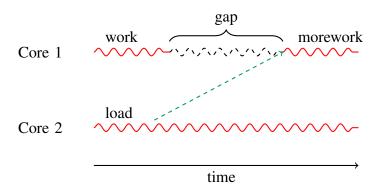

To maximize throughput on modern parallel hardware, the programmer must ensure that all cores are working at all times. But achieving this is difficult; due to slow memory accesses and data dependencies, multi-core CPUs frequently idle:

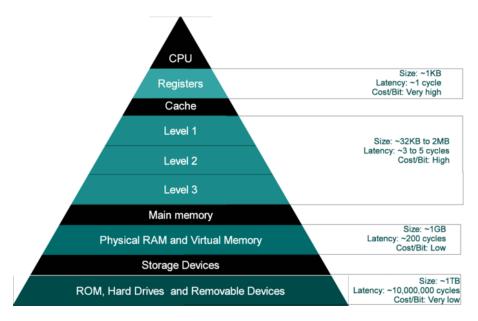

- Main memory is slow to access and could lead to processors idling. If the processor needs to fetch data, ideally the data should be located in the cache, which takes just a few cycles to access. However caches are just a few MB in size, whereas the data structures we work with in machine translation are multiple GB in size and do not fit inside. When main memory needs to be accessed, there would be a considerable amount of time where the processor is unable to do any useful work (Figure 1.3). In order to circumvent this, programmers need to miminize memory accesses and reuse memory as much as possible.

- **Data dependencies** between different CPUs also reduces performance. It is often necessary for one of the processors to access data computed by the other. In this case usually one of the cores needs to wait for the other to finish and

<sup>&</sup>lt;sup>8</sup>Adreno 845/Apple A11

<sup>&</sup>lt;sup>9</sup>Titan Black

<sup>&</sup>lt;sup>10</sup>Titan V

in that time no useful work can be done (Figure 1.4). While it is impossible to completely avoid data dependencies, programmers try to minimize them in order to avoid performance degradation.

**Figure 1.3:** Our processors cores need to compute two *workloads*. The processor has access to small amount of fast memory (cache) which allows it to quickly load new data to its registers in order to perform the computation, which serves to complete the first part of the *workload* task (The green dotted line represents memory access). However when the processor needs to go to main memory, in order to fetch the data necessary for the second part of the task *load*, there is going to be a period of inactivity (represented by the black dotted line) where the computation is stalled due to waiting on memory.

**Figure 1.4:** Core one and two have split the *workload*, between each other in order to complete it faster. However, before Core 1 can continue to do *morework*, it needs to wait for the results of the Core 2 computation, which creates a processing gap where core 1 idling. Multiple synchronization points could easily kill any theoretical multi-core performance benefits.

This thesis shows that data structures and algorithms can be designed to substantially improve the speed of machine translation systems on modern parallel hardware, by minimizing slow memory accesses and synchronization points.

#### 1.1 Thesis structure

This thesis demonstrates the value of designing new algorithms to minimize memory accesses in three separate use cases in machine translation. In each I identify performance bottlenecks, <sup>11</sup> related to memory access patterns, and implement an algorithmic solution catered towards a contemporary parallel setting. The first part of my work is focused on statistical machine translation and the final part is focused on neural machine translation.

In Chapter 2, I provide brief background on parallel hardware and machine translation.

In Chapter 3, I introduce a novel **phrase table** for statistical machine translation that scales linearly with the increase of core count. Unlike previous implementations, my design addresses the needs of contemporary hardware by focusing on efficient sequential memory accesses, rather than compression. Using this new phrase table, I achieve 10 times faster decoding speed in parallel setting, largely because of the reduced thread contention (Bogoychev and Hoang, 2016; Hoang et al., 2016).

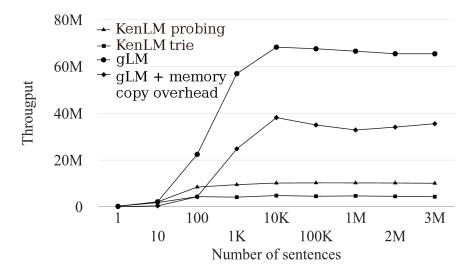

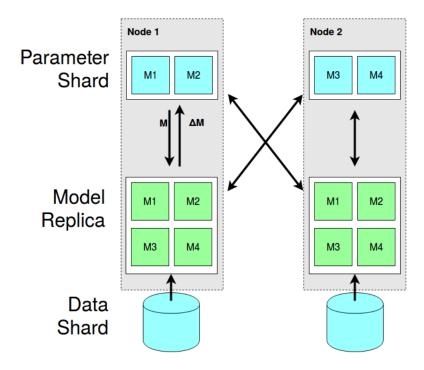

In Chapter 4, I introduce the first GPU **n-gram language model** and I evaluate its performance compared to KenLM (Heafield, 2011), a highly optimized CPU implementation. On the GPU, memory is limited, and every memory access is costly. My language model has a small memory footprint and minimizes the number of memory accesses, which I accomplish using a novel data structure: a BTree-backed trie. This allows for thousands of queries to be executed concurrently on the GPU. The language model achieves 65.5M queries per second in batch mode, which is several times more cost efficient in terms of hardware price than doing the language model queries on CPU (Bogoychev and Lopez, 2016).

In Chapter 5, I show how to improve the speed of **multi-GPU asynchronous training of a recurrent neural machine translation systems** by reducing the frequency of GPU communication. Reducing the communication frequency leads to increased training performance, but worsens the model convergence. I introduce additional methods

<sup>&</sup>lt;sup>11</sup>In this case, and everywhere else in the thesis, the word *performance* is used to mean the speed with which the hardware solves the problem. Where translation quality is concerned I have used *quality*

to tackle the convergence issue and using those I achieve two times faster end-to-end training of a machine translation model at no cost in model quality. Those improvements hold across multiple language pairs and neural network configurations (Bogoychev et al., 2018).

#### 1.2 Contributions

- 1. I have published three papers as a first author (Bogoychev and Hoang, 2016; Bogoychev and Lopez, 2016; Bogoychev et al., 2018) and collaborated on another two (Hoang et al., 2016; Junczys-Dowmunt et al., 2018).

- 2. I have implemented a CPU phrase table for statistical machine translation, that is available both for stand alone usage<sup>12</sup> and as the default phrase table in Moses2 (Hoang et al., 2016), a highly optimized statistical machine translation decoder.<sup>13</sup>

- 3. I have implemented the first GPU based *n*-gram language model. <sup>14</sup>

- 4. I have implemented delayed gradient updates for the Marian NMT toolkit (Junczys-Dowmunt et al., 2018), which permits faster training and helps very large models achieve a reasonable mini-batch size.

- 5. I have worked on the problem of multi-node neural network training on computational clusters with varying connection speed. Together with my collaborators we have implemented a design that minimizes the communication between nodes in order to achieve maximum training speed.

<sup>&</sup>lt;sup>12</sup>https://github.com/XapaJIaMnu/ProbingPT

<sup>&</sup>lt;sup>13</sup>https://github.com/moses-smt/mosesdecoder/

<sup>&</sup>lt;sup>14</sup>https://github.com/XapaJIaMnu/gLM

## **Chapter 2**

# Parallel programming and Machine Translation

In the 1960s and 1970s, two important trends for the development of computer hardware were observed: Moore's law (Moore, 1965) and Dennard scaling (Dennard et al., 1974). The former establishes that the number of transistors on chips would double every 1.5 years and the latter that the performance per watt would grow exponentially at roughly the same rate. Those laws have influenced tremendously the field of computer science, because they predicted that the performance of processors would increase over the years. Software would run faster just by putting it on a newer processor. Moore's law had to be revised several times, because the growth rate it predicted originally decreased over time, but Dennard scaling started to break down completely around 2005-2007 (Figure 2.1). There are several reasons for that:

- 1. With the increased voltage and transistor density on a single chip, it became impossible to dissipate the heat quickly enough (Olukotun et al., 1996).

- 2. With the increased logic circuits and components on a single chip, it became impossible to hide the delay in communication between gates placed physically far away from each other. In order to solve this problem, a greater percentage of the increased transistor count go towards wiring, rather than additional logic gates (Olukotun et al., 1996). A more efficient use of the extra circuits available is to put them to use in an extra processor core. Putting the extra circuits in an additional core allows for overall higher theoretical performance of the new processor, but the burden for achieving it is placed on the programmer.

- 3. There are physical limits on the delay between logic gates: Signal can't pass

100000 End of Moore' 10000 Am-I aw Performance vs. VAX11-780 dahl's ⇒ End of Law 2X / 1000  $\Rightarrow$ 20 yrs Dennard 2X / Scaling 6 yrs 100 (12%/yr) Multicore RISC 2X / 3.5 CISC yrs 10 2X / 3.5 yrs (23%/yr) (22%/vr)

through them faster than the speed of light (McFarland et al., 1995).

**Figure 2.1:** Single core CPU performance on a simple Integer benchmark (SPECintCPU) compared to a 1977 VAX 11-780 processor. Single core scaling breaks down completely after 2015. Image source: Hennessy and Patterson (2018)

1995

2000

2005

2010

2015

Furthermore the nature of the workload has changed the past 20 years. Greater processing power and advances in hardware have given birth to the era of big data. In this era, single instruction, multiple data (SIMD) workloads are increasingly common and multi-core processors are better suited for those. This development, together with the aforementioned difficulties in scaling single-core processors, has swayed chipmakers in designing hardware that is better suited to those workloads: multi-core and massively parallel (vector) processors.

#### 2.1 Parallel hardware

980

1985

1990

Parallel hardware has been conceived for the first time in the mid-1950s and over half a century has become completely integrated even in the most basic consumer level hardware. Parallelism in hardware is found on multiple levels: On a single chip, on a single machine, and on a single network.

#### 2.1.1 On a single chip

**Superscalar architecture** Contemporary processors are capable of executing multiple instructions concurrently. There are several ways to take advantage of those capa-

2.1. Parallel hardware 21

#### bilities:

• In software through out-of-order execution where multiple instructions can be executed in any order as long as this doesn't influence final outcome.

- In the processor itself by speculatively executing branches in order to avoid stalls.

- By using hyperthreads and letting the OS schedule additional work on the processor. I will revisit the concept of hyperthreads in detail in Chapter 3.

Identifying instructions that can run in parallel is, however, a difficult task and frequently the superscalar capabilities are underutilized.

**Symmetric multiprocessors** Symmetric multiprocessors are the most common type of parallel hardware that is used today. They are called symmetric, because as far as the programmer is concerned, all CPUs are equal and have equal access to the main memory. They can be used for any type of parallel operations from multiple instructions, multiple data (MIMD), such as producer-consumer problem to single instruction, multiple data (SIMD), such matrix multiplication.

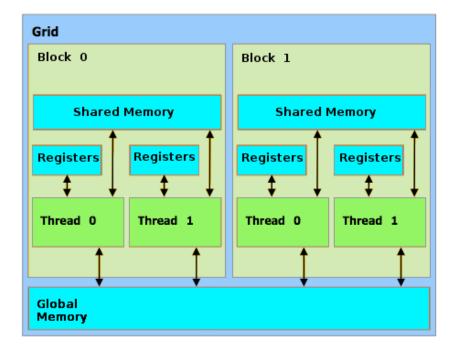

Massively Parallel hardware Massively parallel hardware is characterized by having a large number of processors on a single chip, which are usually not completely independent. For example, Nvidia Pascal Titan X is a graphic processing unit (GPU) that contains 3,584 cores that are controlled by 28 streaming multiprocessors, which means at most 28 different instructions can be executed at a time. Another name used for this type of hardware is **vector processor** and they are specifically designed for SIMD workloads. Individual GPU cores are simple, lacking complicated branch predictors or caches, but because of the sheer number of them, collectively they offer much higher theoretical performance than CPUs, given a suitable workload.

Massively parallel architectures share a lot characteristics, because they are designed to tackle SIMD problems, and as such an algorithm that is efficient on one massively parallel architecture is likely to be efficient on another: An algorithm designed for a GPU would map well onto Xeon Phi, a massively parallel CPU board with 57-72 cores manufactured by Intel.

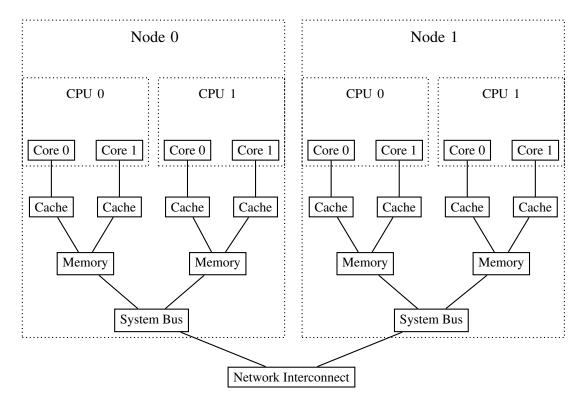

#### 2.1.2 On a single Machine

Most workstation class computers nowadays come with independent CPUs and multiple GPUs. The CPUs are connected through a very fast interconnect and appear to the programmer in the same way a symmetric multiprocessor would. However as the RAM is split between the CPUs (Figure 2.2) accessing memory that was processed by a different physical CPU is more expensive (For precise numbers refer to Table 2.1). The same applies to use multiple GPUs in the computation: While an additional GPU offers theoretically doubled performance, in practise it is difficult to achieve it because of the large cost (Table 2.1) of inter GPU communication. I look specifically at multi-GPU scaling in Chapter 5.

#### 2.1.3 On a single network

Just as we can have multiple computational units within a single machine, we could have multiple machines connected over a network forming a **distributed** computational cluster. Computational clusters allow for potentially thousands of GPUs and CPUs to work together towards a common computation, however programming for them is challenging: When working with distributed hardware memory access to different units is non-uniform (Figure 2.2)—that is to say, memory is organized in a hierarchical manner where the latency of remote memory is much higher than the latency of local memory and the speed of local memory is much higher than the speed of remote memory. As such, algorithms must be designed in a manner that minimizes accesses to the slow remote memory.

### 2.2 Why parallel programming is hard

There is a subset of programming problems which are labelled *embarrassingly parallel* that exhibit perfect parallelism. They are characterized by lack of communication between cores, which means that no synchronization points are necessary and the cores operate completely independently. An example of perfectly parallel problem is neural network **inference**, where one can generate predictions using the neural network on as many cores as they want in a SIMD manner since the neural network parameters are read only and there is no inter-core communication. Unfortunately, most real world problems require communication in parallel setting and also exhibit difficulties with balancing work evenly between the available computational units, which is notoriously

23

**Figure 2.2:** Typical memory hierarchy on a computational cluster. Each Node on the cluster has multiple CPUs, each of them has multiple physical cores. Each core has local cache. Each CPU controls a portion of the system memory. Different CPUs communicate to each other's memory through the system bus and communication speed depends on their physical distance, among other factors. In addition to that all nodes are connected through a network and can access each-other's memory resources, but at a much higher latency and lower speed.

difficult (Perrone, 2009).

Parallel programming requires programmers to deal with issues that do not exist in single threaded setting:

Data hazards occur when data written by one thread needs to be read by another. When those threads are scheduled on different cores (or processors) writes need to be propagated through memory in order to be visible to everyone, which requires explicit synchronization or use of atomic instructions, both of which are expensive: Synchronization leads to CPUs idling, and atomic instructions block any sort of instruction-level parallelism, which is very important for nowadays' superscalar processors to achieve peak performance (Schweizer et al., 2015).

**Load balancing** is the problem of distributing the workload evenly across multiple available computational cores. This part is particularly challenging because a lot of commonly used algorithms are inherently sequential and it is not easy to

extract independent pieces of work that can be done in parallel.

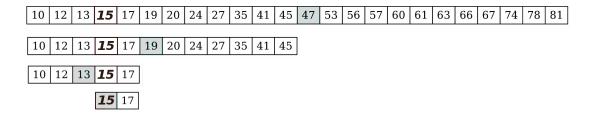

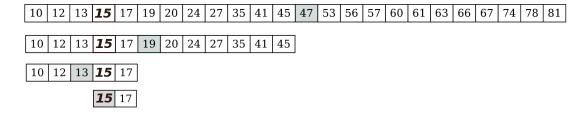

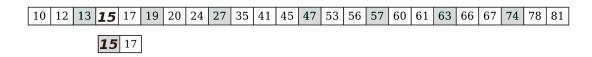

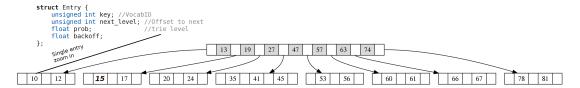

For example, binary search is a widely used search algorithm that is inherently sequential and as such it is impossible to load balance it between multiple processors. Figure 2.3 shows querying a sorted array of numbers for the position of the number 15. In binary search, at each time step, we take the middle element of the array and we compare it to the number queried. Based on that we discard the half of the array that we know does not contain our number and we repeat the process. Eventually we narrow down the array to two elements and we manage to find our number with just  $\log_2(n)$  comparisons and  $\log_2(n)$  time, which is much faster than a full scan of the array, however because the input of each step depends on the output of the previous step, parallelization is not possible.

**Figure 2.3:** Execution of a binary search for key 15. Each row represents a time step and highlights the element compared to the key. Finding key 15 requires four time steps and four comparisons.

On a parallel hardware however we have to change the algorithm to k-ary search in order to take advantage of the architecture. In k-ary search, we essentially split the array in k blocks where k is the number of parallel executing cores and we perform k binary searches in parallel (Figure 2.4). While this solution performs more comparisons in total:  $(k-1)\log_k(n)$ , they are executed in parallel by k-1 devices, resulting in overall runtime of just  $\log_k(n)$ . As k-ary search maps better to the parallel architecture, it performs the search over the same array in just two timesteps, as opposed to four.

**Figure 2.4:** Execution of K-ary search with the same input as Figure 4.5, for K = 8. The first time step executes seven comparisons in parallel, and the query is recovered in two time steps.

#### **2.2.1 Memory**

In this section, I give an overview of memory and why its efficient usage is the key to fast computation.

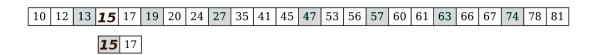

#### 2.2.1.1 Memory speed

Even in perfectly parallel setting, the programmer must be very careful of the memory usage. Memory speed grows 50% slower than compute speed (Carvalho, 2002) and it often bottlenecks execution time (Patterson et al., 1997). Table 2.1 and Figure 2.5 show approximate time in which CPUs and GPUs need to wait to access a piece of memory. Memory accesses are especially important in parallel and massively parallel setting, because each core or GPU has memory associated with it and accessing remote memory is much slower than accessing local memory (Figure 2.1). Main memory is large and cheap to produce, but accessing it is slow. On the other hand registers and CPU caches much faster, but small and expensive to manufacture (Figure 2.5). In order to avoid expensive trips to main memory, programmers have to carefully design their application so that it minimizes memory accesses and reuses memory where possible. Often, optimizing parallel applications is a matter of reducing memory accesses and where this is not possible, rearranging them in such a manner that one memory access can be used by multiple cores at the same time.

Figure 2.5: Memory hierarchy in the CPU world. Source: Andalam et al. (2013)

| CPU         |         | GPU         |         |  |

|-------------|---------|-------------|---------|--|

| Memory type | Latency | Memory type | Latency |  |

| Register    | 0       | Register    | 0       |  |

| L1 cache    | 4       | Shared      | 4–8     |  |

| L2 cache    | 10      | Global GPU  | 200-800 |  |

| L3 cache    | 40      | CPU         | 10K+    |  |

| Remote L3*  | 80      | Remote GPU  | 22K+    |  |

| DRAM        | 330+    |             |         |  |

| Remote DRAM | 660+    |             |         |  |

**Table 2.1:** Latency (in clock cycles) for accessing different types of CPU and GPU memory. Estimates are adapted from Intel Corporation (2009); NVIDIA Corporation (2015) and also depend on several aspects of hardware configuration. Time for accessing remote GPU devices or DRAM associated with different CPUs is more than twice as slow as accessing local memory.

#### 2.2.1.2 DRAM bursts and coalesced memory accesses

In order for a programmer to take full advantage of the available memory bandwidth, he/she needs to be mindful of the DRAM burst effect. It is observed that if an application accesses a piece of memory, it is likely that it would also need to access adjacent pieces in the very near future. Because of that main memory is designed to fetch surrounding bytes, together with the requested bits. This effect is known as DRAM burst and its size varies between architectures, but is usually between 32 and 256 bytes. This is the reason why random memory accesses are much much slower than consecutive ones: The consecutive ones can be made essentially for free, as long as they fit within the DRAM burst, whereas random accesses can't make use of all the available memory that has been fetched. In the GPU programming world, where it is usually the case that one thread operates on one unit of data, random memory accesses are particularly harmful, just because there are a lot more of them happening in parallel. In this case it is very important make sure that consecutive threads operate on consecutive pieces of memory, which makes the memory accesses **coalesced**. On the other hand if memory accesses from consecutive threads are not consecutive, the memory access pattern is called **strided**.

<sup>\*</sup>Remote L3 refers to accessing cache line shared with a different core that is physically located on the same chip.

27

#### 2.2.1.3 Data sharing

Data sharing is also problematic: Sharing reads and writes between different threads requires deterministic behaviour which can only be achieved with locking. Locking is expensive because it both stalls some of the cores and involves an expensive context switch to kernel space. For example, in a multi-threaded web crawler where all threads read URLs from a the same queue, every time a thread reads a URL, it needs to be removed from the queue. To ensure that each thread will get a different URL, the queue must be locked before it is modified.

#### 2.3 Machine Translation

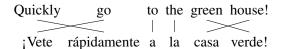

Machine translation is the problem of performing an automatic translation from one language to another, for example, the English sentence *Quickly go to the green house!* into Spanish *¡Vete rápidamente a la casa verde!* This is achieved by first training machine learning models on large amount of parallel sentences and then using those models to predict the translations of unseen data.

#### 2.3.1 Statistical Machine Translation

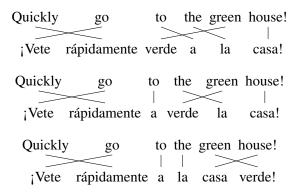

In statistical machine translation, we model the problem as a process of first translating individual words or phrases, and then reordering these translations as shown on example 2.6.

**Figure 2.6:** English-to-Spanish translation with word-to-word correspondence.

Since there may be many possible translations of a word or phrase, we require a probabilistic model to choose between them – a translation model. The translation model  $P(f \mid e)$  provides the probability of a source language phrase f is the translation of the target language phrase e. We combine it with a language model P(e) that gives the likelihood of the sentence e occurring in the target language. Since a phrase table does not contain all possible phrases, the decoder may **reorder** some words in order to attempt to produce a more fluent translation (in practise the decoder may also reorder whole phrases around if it deems it necessary to produce a more fluent output). In

order to find the highest scoring translation  $\hat{e}$ , we need to perform a search over all possible reorderings E(f) (Equation 2.1).

$$\hat{e} \propto \underset{\text{Search}}{\underbrace{\arg\max_{e \in E(f)} P(f \mid e)}} \times \underbrace{P(e)}_{\text{LM}}$$

(2.1)

### **2.3.1.1** Translation model: $P(f \mid e)$

The **Translation Model** is the P(f | e) part of equation 2.1. It provides translations between words of phrases across languages. Languages rarely have one-to-one mappings so we have to deal with a probability distribution over possible translations. For example, the English word go could translate into Spanish as vaya, vete, va, ir or a myriad of other present tense conjugations due to the more rich tense system in Spanish. The job of the translation model is to provide us with the probability of each possible mapping of the words or phrases across the languages in concern.

Working through my small example, let us imagine how a simplified phrase table would look just for the verb "go" and the phrase "go to the":

| English   | Spanish   | Probability |

|-----------|-----------|-------------|

| go        | ir        | 30%         |

| go        | va        | 30%         |

| go        | vaya      | 10%         |

| go        | ve        | 10%         |

| go        | vete      | 10%         |

| go        | va        | 10%         |

| go to the | vaya a la | 30%         |

| go to the | vaya al   | 30%         |

| go to the | vas a la  | 15%         |

| go to the | vas al    | 15%         |

| go to the | vete al   | 5%          |

| go to the | vete a la | 5%          |

**Table 2.2:** An extract from a Spanish-English phrase-table for the word "go" and the phrase "go to the". In this case English is the source language f and Spanish is the target language e.

This is the phrase table ambiguity that occurs just for quarter of the words in the example sentence. Phrase tables' size could reach hundreds of gigabytes in size (Lopez,

29

2007, 2008; Germann, 2014; Bogoychev and Hoang, 2016) and its query speed is crucial in order to achieve fast decoding speed. In Chapter 3, I show how my improved phrase table design leads to order-of-magnitude increase in decoding speed in parallel setting.

#### 2.3.1.2 Language model: P(e)

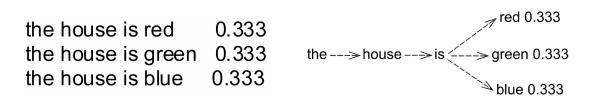

The **Language Model** is the P(e) part of equation 2.1. The translation model has provided the possible translations of the phrases, but there is no way of knowing which ones would be the most appropriate. The language model is a statistical representation of a language which captures likely sequences. During translation we can use the language model to choose the most likely permutations from the translation model that constitute fluent speech in the target language. N-gram language models with a smoothing strategy (Chen and Goodman, 1999) are most commonly used in statistical machine translation. Here N refers to the maximum context window size of the language model.

If we don't have the full sentence in the phrase table, we build our translation out of smaller phrases that we have seen already in our training data. However as languages do not have a monotonic or one-to-one mappings, a single source word is often translated into multiple target words depending on the context. In order to disambiguate, we require a language model to tell us how likely the sequence we have produced is and to potentially reorder words in some phrases in order to achieve a more natural translation. In my example, if my phrase table does not contain the phrase to the green house  $\leftrightarrow$  a la casa verde, we would have to use unigram translations. In this case (and assuming all other parts of the sentence are built correctly) we would build the following translation:

This sentence is not grammatical, due to the words casa and verde appearing in the wrong order and would be given a low score by the language model. Our translation system would attempt to produce a better candidate sentence by trying out different permutations of the target words to be scored by the language model as shown on Figure 2.7.

This process would be repeated with every phrase used to construct the sentence,

Figure 2.7: Example permutations of the Spanish translation of to the green house.

thus thousands of similar permutations need to be produced. In practice there is a limit on the distance any given word can move in order to reduce the search space.

On average, more than 700,000 language model queries are done per sentence decoded (Heafield, 2013) which takes up more than half of the wall clock time (Green et al., 2014). In statistical machine translation, the language model is the most important component for achieving fluent target side sentences and thus researchers and industry use the largest model they have (or the largest model their system can fit in memory). Google are known to use an *n*-gram language model with 2 billion tokens and more than 300 billion *n*-grams (Brants et al., 2007). In Chapter 4, I show how we can use GPUs to accelerate *n*-gram language model queries.

#### **2.3.1.3** Search: $\hat{e} = \arg \max_{e \in E(f)}$

Search is the  $\hat{e} = \arg\max_{e \in E(f)}$  part of equation 2.1. For any given sentence all possible permutations of the translation model outputs are scored using the language model and the translation model. The sequence with the highest probability is the chosen translation. The search space increases exponentially with sentence length, because of the one-to-many translation mapping and the possible phrase permutations. Searching exactly for the best translation involves producing hundreds of thousands translations that are evaluated by the language model (Koehn, 2010). In order to make it tractable various pruning methods are used (Tillmann and Ney, 2003; Chiang, 2007), which find an approximate solution. Unfortunately, while those approximation techniques significantly reduce the computational cost, they are also inherently sequential and hard to parallelise. Because this thesis does not focus on search, I do not go into further detail here.

31

#### 2.3.2 Neural Machine translation

Neural machine translation does not employ any of the statistical methods from statistical machine translation. Instead it employs a neural network to directly model  $P(e \mid f)$  by conditioning every single target word  $e_i$  on all previously produced target words  $e_1, ..., e_{i-1}$  and the full input sequence f:

$$P(e \mid f) = \prod_{i=1}^{|f|} P(e_i \mid e_0, ..., e_{i-1}, f_1, ..., f_{|f|})$$

The most popular architecture, designed by Bahdanau et al. (2014), is a bidirectional long-short term memory (bi-LSTM) recurrent neural network (RNN) with an encoder, decoder and attention mechanism. The details of these models are not crucial to understanding this thesis, so I do not describe them in detail here. Neural network parameter optimisation, or **training**, is performed using stochastic gradient descent, most commonly using **mini-batches**, tiny subsets of the training data: The training data is split into many mini-batches and then for each of them we compute a forward pass through the network, to get the predictions and the error, and a backward pass in order to get the gradient and update the parameters. As such, neural network training is roughly three times more expensive per sentence compared to inference, therefore parallelising training across multiple GPUs is important in order to reduce training times. Chapter 5 explains in details neural network training.

Neural machine translation training is very computationally expensive due to the large number of model parameters – over 200 million that form up the weight matrices<sup>1</sup>, as well as the large number of sentences that are passed through the network during training – over 100 million.<sup>2</sup> Training those systems takes weeks on multiple GPUs (Wu et al., 2016), therefore training speed is a limiting factor for neural machine translation: The large amount of time it takes to train the model to convergence limits the amount of experiments that are able to be completed, the training data that is able to be used and the size of the neural network.

Goyal et al. (2017) have shown that neural network training can be substantially sped up by increasing the mini-batch size and using large amount of GPUs (256). They train ImageNet, a large scale image classification task by Deng et al. (2009), in just one hour, however the approach they take does not translate directly to the neural machine

<sup>&</sup>lt;sup>1</sup>Measurement taken from the Haddow et al. (2018) models.

<sup>&</sup>lt;sup>2</sup>The corpora are actually much smaller than that, but they are passed through the neural network multiple times

translation setting, because of the different type of neural network (convolutional vs recurrent) and the different type of data. In Chapter 5, I show how we can substantially increase the speed of neural machine translation training, by applying some of the methods by Goyal et al. (2017) and my own original work.

#### 2.4 Conclusion

In this, chapter I have discussed the physical limitations that have ended single core scaling and thus driven hardware manufacturers towards parallel and massively parallel devices. Multi-core and massively parallel devices work best with small data structures in compute heavy workloads that require little to no synchronization, which is at odds with the workloads typical for machine translation. Statistical machine translation works with large data structures that put a lot of strain on the memory and multi-device neural machine translation training requires frequent synchronization points. In the next three chapters, I show how we can extract better performance from modern parallel and massively parallel hardware in both statistical and neural machine translation setting.

## **Chapter 3**

# Phrase table for for symmetric multiprocessors

Phrase tables are the most basic component of a statistical machine translation decoder, containing the parallel phrases necessary to perform phrase-based machine translation. A phrase table is a dictionary that maps source phrases to target phrases. It is used in statistical machine translation to produce a list of possible target phrase translations, given a source phrase. Phrase tables typically reach hundreds of gigabytes in size, and Lopez (2008) describes phrase tables that reach half of terabyte in size. A decade ago it was prohibitively expensive for a phrase table of this size to reside in memory, even if hardware supported it: a gigabyte of RAM cost about a 100 USD in 2006, compared to 5 USD in 2018. Because of that for a long time machine translation was considered a big data problem and the engineering efforts were focused on reducing the memory footprint. Phrase tables were implemented using a number of different data structures which all tackled the memory usage problem in a different manner:

- Zens and Ney (2007) developed a prefix tree (commonly known as a trie; Fred-kin, 1960) based phrase table that drastically reduces the memory usage. The phrase table was designed with the idea that the trie is to be an external data structure residing on disk, as it is too big to be loaded in memory in its entirety and subsections of it are only loaded on demand.

- Callison-Burch et al. (2005); Zhang and Vogel (2005); Lopez (2007); Germann (2015) developed suffix array based phrase tables, which work directly with the parallel corpora, extracting target phrases on the fly, in order to enable easier addition of new data and keep memory usage low. This is great in terms of flex-

ibility and memory usage, but comes at the cost of speed, as the suffix arrays are searched using binary search, which requires  $log_2(T)$  random memory accesses where T is the number of tokens in the parallel corpora, which is detrimental to performance.

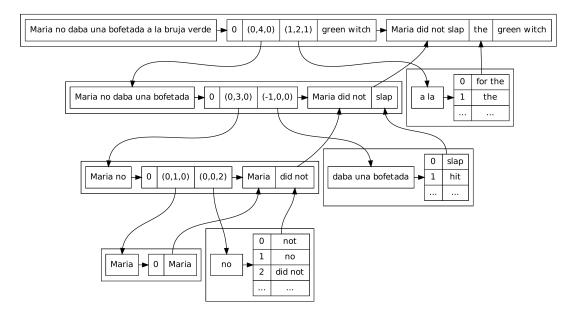

- Junczys-Dowmunt (2012) developed another phrase table that focuses on compression and small memory footprint. It uses phrasal rank encoding (Figure 3.1), which can be viewed as a form of phrase level byte pair encoding (Gage, 1994). The method recursively encodes bigger strings as a composition of several smaller ones until only small units remain. Source phrases that do not expand further point to a list of target phrases to which they correspond, ranked by probability. Figure 3.1 shows shows the retrieval process for the source phrase *Maria no daba una bofetada a la bruja verde* from the phrase table.

- Querying the initial source phrase returns two triplets of numbers, along-side plain text *green witch*. This means that for reconstructing the target phrase we need to query two subphrases, defined by those triplets, as well as concatenate the resulting target phrases with *green witch*, which is stored as plain text here because it only occurs once in the corpora.

- The span {0,4,0} encodes the following information: The difference of indexes between the start the source phrase and the target subphrase, the distance from the right subphrase to the end of the encoded phrase and the rank of the target phrase among all target phrases that correspond to this context. Using this information we identify the next subphrase that needs to be queried, Maria no daba una bofetada and obtain a corresponding pair of triplets.

- We follow the next triplet to first get *Maria no* and later two separate unigram queries of *Maria* and *no*.

- *Maria* has only one translation so it has rank 0 and we obtain the corresponding target phrase *Maria*, however *no* has multiple possible translations. This is why the triplet corresponding to *no*, {0,0,2} identifies that we are interested in the translation ranked 2, *did not*.

- The procedure is repeated until all subphrases reconstructed. The cost of querying this phrase table during decoding is potentially exponential in terms of sentence length as phrase based decoding proceeds left-to-right

Figure 3.1: Phrasal rank encoding. Figure taken from Junczys-Dowmunt (2012)

and will query all subphrases of a sentence. Extensive caching is used in order to avoid repeated subphrase expansions.

In order to further reduce memory footprint, minimum perfect hashing (Nick Cercone, 1983) is used to hash phrases to their expansions and on top of that bitaligned Huffman encoding is used to further compress the phrases.

The rest of the chapter is structured as follows: First, I describe the problems with the current implementations. Then, I describe my own implementation that addresses the aforementioned shortcomings and finally I evaluate the performance of my novel phrase table against existing implementations.

### 3.1 Problems with current implementations

RAM prices have dropped 20 times over the past decade and high performance server machines have hundreds of gigabytes of memory. For those machines it is no longer needed to sacrifice query performance in favour of compression techniques such as the ones described above. The implementation of Junczys-Dowmunt (2012), which was the state of the art phrase table in terms of both speed and space usage in 2012 is slow on modern parallel hardware because:

Many random memory accesses Phrasal rank encoding, together with Huffman encoding make the implementation of Junczys-Dowmunt (2012) extremely space efficient, but at the cost of speed, because of the potentially exponential number of random memory accesses necessary to reconstruct a single phrase as shown on Figure 3.1. As discussed earlier, large number of random memory accesses make poor use of the DRAM burst, which results in very poor memory bandwidth.

Caching is slow in multi-threaded setting To make queries faster, Junczys-Dowmunt (2012) uses extensive caching. The cache is implemented as a dictionary of source phrases and the corresponding target phrases. To conserve memory all threads used during decoding share the same cache, so the cache needs to be locked when updated. Therefore, when using more than 8 threads during decoding, performance goes down due to the cost of locking.

#### 3.2 ProbingPT

I have designed a new phrase table called **ProbingPT** based on linear probing hash table (Peterson, 1957) for storage and lock-free querying, in order to deliver high performance in modern use cases where memory is not limited. My goal in design was to eliminate the necessity for cache by using data structures that minimize random memory accesses.

Linear probing hash table H is a data structure, based on an array A, that maps a key k to a corresponding value v. A hash function  $h:k\to\mathbb{N}$  determines the memory location where v is going to be stored inside the hash table. If several different k point to the same memory location, there will a hash **collision** that needs to be resolved. In order to identify whether a key collision has happened or if we are trying to insert a duplicate entry, we store a fingerprint, the result of a *different* hash function  $h':k\to\mathbb{N}$  together with v. In a linear probing hash table, linear probing refers to the collision resolution strategy of the hash table, where if k points to a memory location in k that is already occupied by a different key, the next available memory location is used instead. This is very efficient, because those memory locations would already be loaded from main memory due to the DRAM burst effect.

When a linear probing hash table is queried we check if k exists at its corresponding memory location. If the memory location is unoccupied, then we can conclude that k and its corresponding v are not found in the table. If the memory location is occupied

3.2. ProbingPT 37

we verify that the k queried is the same as the one found at the memory location and not a product of collision. If there is a mismatch, we proceed to linearly traverse the phrase table until either we encounter a match of our k in which case we return the corresponding v, or we reach an empty space or the end of the hash table. The latter two cases mean that k and its corresponding v are not in the hash table.

I use an existing linear probing hash table implementation (Heafield, 2011). Linear probing hash provides O(1) search time, has a very small overhead per entry stored and is shown to be very fast in practice (Peterson, 1957).

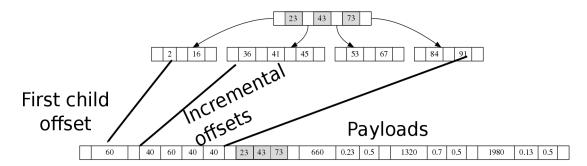

The phrase table consists of three arrays: The first H contains a probing hash table that maps hashes of source phrases to a memory location in the payloads array P, which contains phrase probabilities, word alignments key, and optionally lexical reordering score, a common feature used in statistical machine translation. The third array is another hash table A that contains word alignments. Since there are about a 1000 unique word alignments for the hundreds of thousands of phrase pairs I store them in a separate hash table and in the payloads array I store an extra key for each target phrase that points to its corresponding alignment in the hash table. Hashes of the source phrases are used as keys. The query algorithm goes as follows:

- 1. The translation of a source phrase is requested from the decoder.

- 2. The source phrase is hashed to produce a key *k* for which *H* is queried. If it doesn't exist, "NOT FOUND" is returned to the decoder. This is the first random memory access that the phrase table makes.

- 3. If it does exist, the hash table returns the memory location within *P*. This memory location is where all target phrases, corresponding to this source phrase are stored.

- 4. The first few bytes at the memory location that was previously identified contain information about the number of target phrases and the number of bytes they occupy. This is the second random memory read. Since everything is laid out consecutively in *A*, this DRAM burst also loads the memory for the target phrases that are about to be extracted.

- 5. Then, for each target phrase, the phrase table extracts the scores, the alignments and the tokens and returns them in separate arrays so they are easily used by the decoder. All of those elements with the exception of the alignment scores are laid out consecutively in the payloads array. The alignment scores are extracted

from A. For each target phrase there is potentially one additional memory access to A for the alignment scores.

My new phrase table phrase table address the shortcomings of previous implementations:

Few random memory accesses I have reduced the number of random memory accesses from potentially exponential in terms of phrase length, to just two: One for the large probing hash table and one for the payloads array. My phrase table also also has one additional memory access per target phrase, because it needs to fetch the alignment information from a separate hash table. That hash table, however, is small enough (20-30 KB) to fit in the L1 or L2 cache of any modern processor, which makes accessing it quite cheap: If the memory location accessed is already in cache, the cost of random memory access is not at all high: just 4-10 CPU cycles, compared to 300+ for DRAM.

**Caching is now redundant** The phrase retrieval procedure of my phrase table is simple and doesn't involve large number of memory accesses, which makes caches unnecessary. This makes the phrase table multi-threading friendly, because there is no need for locking or synchronization of different threads.

#### 3.2.1 Integrated lexical reordering

Lexical reordering scores, associated with every single source-target phrase pair, are frequently used in Moses (Koehn et al., 2007) as a feature function, but they are stored separately from the phrase table inside a reordering table. Since those scores are associated with every single phrase pair, it is possible to attach those scores to the phrase table's entries. Doing so reduces both memory usage and memory accesses: We no longer require a separate hash table for the source/target phrases that the lexical reordering scores are associated with, as I reuse the key from my phrase table. Extracting lexical reordering scores no longer incurs the penalty of additional memory accesses, as querying is tied to the phrase table query and all related scores would be fetched with the same DRAM burst, because they are stored consecutively. To my knowledge, this is the first phrase table implementation that incorporates lexical reordering table.

The phrase table is part of upstream Moses<sup>1</sup> but it can also be used standalone.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>https://github.com/moses-smt/mosesdecoder

<sup>&</sup>lt;sup>2</sup>https://github.com/XapaJIaMnu/ProbingPT

#### 3.3 Experimental setup

For the performance evaluation I used French-English model trained on 2 million EU-ROPARL sentences. I used a KenLM (Heafield, 2011) language model and cube pruning algorithm (Chiang, 2007) with a pop-limit of 400. I time the end-to-end translation of 200,000 sentences from the training set. All experiments were performed on a machine with two Xeon E5-2680 processors clocked at 2.7 Ghz with total of 16 cores and 16 hyperthreads and 290 GB of RAM.

Hyperthreads are Intel's way of implementing simultaneous multi-threading, a technique that improves the efficiency of modern superscalar processors. Superscalar processors can execute more than one instruction in parallel, provided such instructions are scheduled. Hyperthreads expose additional CPU cores to the OS, which are indistinguishable from actual CPU cores. A 16 core, 16 hyperthread processor would appear to the OS as a 32 core processor. This allows for the OS scheduler and applications to schedule more instructions to the processor which ensures that there would be enough instructions available to take advantage of the superscalar architecture. It is important to note that hyperthreads do not always increase performance. In scenarios where there is high level of lock contention, the introduction of additional threads in the workload will make the performance go down.

In all of my figures "32 cores" means 16 cores and 16 hyperthreads.

#### 3.3.1 Decoders

I use two different decoders for my experiments: The widely used Moses machine translation decoder and *Moses2*, a redesign of Moses focusing on speed (Hoang et al., 2016). I benchmark using Moses to show the speedup my implementation offers as a drop-in replacement to existing phrase tables in the widely used decoder. Unfortunately, Moses has major multi-threading problems, due to its extensive usage of **std::locale**, which invokes a global lock. As such, Moses is a poor framework for measuring the multi-threading performance of my phrase table, as the underlying multi-threading already cause high lock contention at high thread count. I used the highly optimized *Moses2* to show the speed my phrase table can achieve when it is running on a decoder optimized for multi-threading. Furthermore the *Moses* API made it difficult to include integrated lexical reordering and it is only a feature in *Moses2*.

#### 3.3.2 PhraseTables

In my experiments I compare ProbingPT against CompactPT (Junczys-Dowmunt, 2012). There are currently two other phrase tables: PhraseDictionaryOnDisk, a multi-threading enabled implementation of the Zens and Ney (2007) phrase table and PhraseDictionaryMemory, an in-memory phrase implementation of the work of Zens and Ney (2007) using STL data structures. Junczys-Dowmunt (2012) has shown that CompactPT is faster than both implementations of the Zens and Ney (2007) in all settings. Based on this I focus on comparing ProbingPT against CompactPT.

ProbingPT and CompactPT produced nearly identical translations under the same decoder. In my tests 3 out of 200,000 sentences slightly differ in their translation. This is expected according to Junczys-Dowmunt (2012) because CompactPT may reconstruct a phrase erroneously in a few edge cases.<sup>3</sup> Since my phrase table produces the same translations as both implementations of Zens and Ney (2007), I conclude my implementation is correct and can be used as drop-in replacement for CompactPT.

#### 3.4 Results

| Phrase table                | Size   |

|-----------------------------|--------|

| ProbingPT                   | 5.8 GB |

| ProbingPT + Reordering (RO) | 8.2 GB |

| CompactPT                   | 1.3 GB |

| CompactPT RO                | 0.6 GB |

**Table 3.1:** Phrase table sizes

CompactPT which is designed to minimize model size has naturally lower model size compared to ProbingPT. However the extra RAM used is only 2% of the 290 GBs available on my test system which is insignificant.

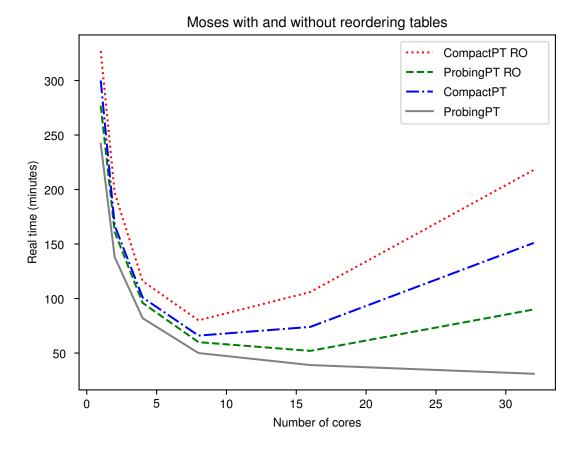

Figure 3.2 shows performance comparison of two systems with CompactPT based reordering tables that differ in the phrase table used. The best performing ProbingPT system here delivers about 30% better performance compared to the corresponding CompactPT system. We see that the CompactPT system doesn't improve its perfor-

<sup>&</sup>lt;sup>3</sup>Personal correspondence

3.4. Results 41

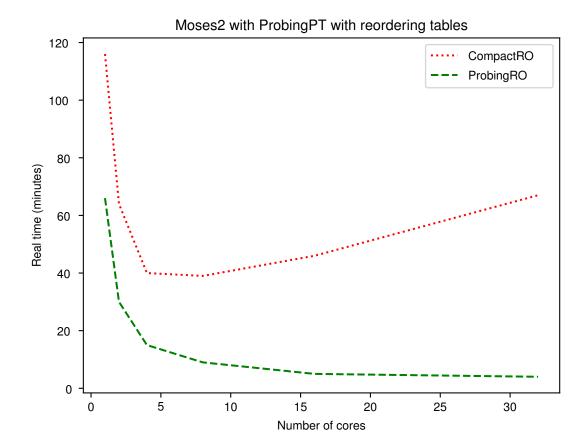

**Figure 3.2:** A comparison of CompactPT and ProbingPT's time to translate the dataset with different core counts. The ProbingPT systems are better than the CompactPT systems, which stop scaling at 8 threads. ProbingPT scales up to 16 threads when a CompactPT based reordering table is also used, but when it is removed, the ProbingPT system continues scaling.

mance when using more than 8 threads, but the ProbingPT one continues to scale further until it starts using hyperthreads.

I hypothesized that the performance of the ProbingPT system on Figure 3.2 is hampered by the inclusion of CompactPT based reordering. Moses doesn't support ProbingPT based reordering and in order to measure the head-to-head performance of the two phrase tables, I also included in the figure the same test using two systems that do not use reordering tables. We can see that ProbingPT model without reordering table consistently outperforms the corresponding CompactPT by 10-20% at lower thread count but the difference grows as much as 5 times in favour of ProbingPT at the maximum available thread count on the system. Comparing the best performance achieved from both system, ProbingPT is capable of delivering twice the performance of CompactPT. It is important to note that ProbingPT's performance always increases with the

**Figure 3.3:** System time comparison of the systems on Figure 3.2. System time is larger in terms of absolute value compared to real time, because it is summed across all threads.

8 threads. We can also see that the ProbingPT based system can even take advantage of hyperthreads, which is not possible with any system that uses CompactPT based table (Figure 3.2). Removing the reordering table from the CompactPT system has a much smaller effect than removing it from the ProbingPT system. This shows that the lexical reordering table only slows down the decoder because it is implemented in a inefficient manner. I can conclude that Moses can achieve faster translation times on highly parallel systems by using ProbingPT.

#### 3.4.1 Why is CompactPT slower?

In the single-threaded case it is likely that CompactPT's many random memory accesses cause it to be slower than ProbingPT, because consecutive memory accesses are much faster due to the DRAM burst effect. When the thread count grows, the

3.4. Results 43

performance gap between CompactPT and ProbingPT widens, because of the locking that goes on in the former's cache. This can be seen from Figure 3.3 which shows the system time used in the experiment on Figure 3.2. System time shows how much time a process has spent inside kernel routines, which includes locking and memory allocations and IO operations. We want to avoid spending time in kernel routines as much as possible, because context switching to kernel space is expensive and runtime spent in there is wasteful in terms of computational resources. The system time used in the CompactPT systems grows linearly until 8 threads and then the growth rate starts increasing at a faster rate widening the gap with ProbingPT. This is also the reason why CompactPT's performance severely degrades when using hyperthreads: the extra threads just spend more time waiting on locks, rather than doing useful work. The ProbingPT system without reordering table on the other hand increases its usage of system time at a linear rate even when using hyperthreads. In the worst case, when using 32 threads, ProbingPT spends 16% of its runtime in kernel routines, whereas CompactPT spends 84% of its runtime there at the same thread count. I can conclude that design of ProbingPT, which focuses on memory throughput rather than compactness, scales very well with the increase of number of threads and is suitable for use in modern translation systems running on contemporary hardware.

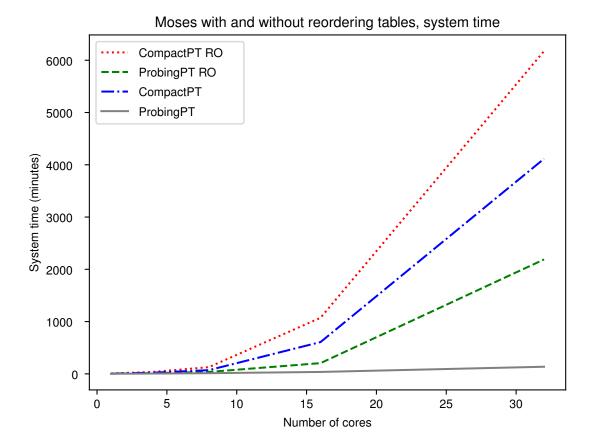

### 3.4.2 Order of magnitude performance improvements with integrated reordering table

As integrated lexical reordering is only available in *Moses2* I conducted an experiment where I compare systems using CompactPT based reordering and ProbingPT integrated reordering (Figure 3.4). The ProbingPT based system is able to translate all sentences in my test set in only 4 minutes, whereas the the system using CompactPT reordering system took 39 minutes. I also observed limited scaling when using CompactPT based reordering: the best performance was achieved at 8 threads. I observe that using lexical reordering table has negligible impact on performance if it is used within ProbingPT. I am not entirely certain which factor contributed more to the increased performance: having a reordering table based on the faster ProbingPT or the reduced IO and computational resources that the integrated reordering table requires. As currently there is no standalone ProbingPT based reordering table I can not say for sure. Nevertheless I achieve 10x speedup by using my novel reordering table within *Moses2* (Figure 3.5).

**Figure 3.4:** *Moses2* comparison between ProbingPT integrated reordering and CompactPT based reordering. Both systems use ProbingPT as a phrase table.

#### 3.5 Evaluation

#### 3.5.1 Profiling the code

I was very surprised of the speedup my phrase table offered, particularly in *Moses2*, because in phrase-based decoding, the number of phrase table queries increases linearly with the length of the sentence. They constitute a tiny fraction of the number of language model queries, which are about 1 million per sentence (Heafield, 2013). To get a clearer understanding of this, I used Google's profiler.<sup>4</sup> I profiled the pair of systems, displayed on Figure 3.4. In the system which has ProbingPT based reordering, the language model is responsible for about 40% of the decoding runtime, compared with only 1% in the *Moses2* system with CompactPT based reordering. In the latter system the runtime is dominated by CompactPT search and **std::locale** locking due to

<sup>&</sup>lt;sup>4</sup>https://github.com/gperftools/gperftools

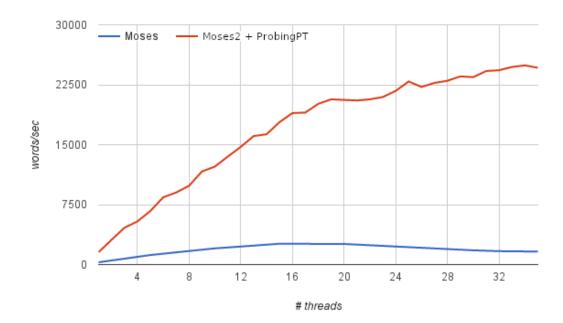

**Figure 3.5:** Comparison between *Moses* and *Moses2* with ProbingPT in terms of words-per-second decoding performance. Image source: Hoang et al. (2016)

the phrase table using string operations during its search.

In *Moses* the difference between using ProbingPT and CompactPT is not so apparent, before we go to higher thread count, because the decoder itself is very slow and hides the phrase table inefficiencies. It is clear that even though the phrase table queries are a small part of the full decoding process, they are enough to slow it down 10 times if no other bottlenecks exist. Using ProbingPT for both the phrase table and the reordering model makes for a compelling combination.

#### 3.6 Conclusion

I conducted a case study of phrase table performance in a statistical machine translation decoder and identified performance shortcomings in existing phrase table implementations: Modern hardware has abundance of memory, but memory speed is still much lower than the CPU's computational power. Therefore in order to take full advantage of the modern parallel hardware we need to minimize memory accesses and remove synchronization points. Having those in mind I designed a new lock free phrase table, that maximizes memory bandwidth and achieved 10x performance improvement over existing implementations. My phrase table is the central piece of the *Moses2* decoder

and is available as a standalone software that can be used by other researchers.

#### Chapter 4

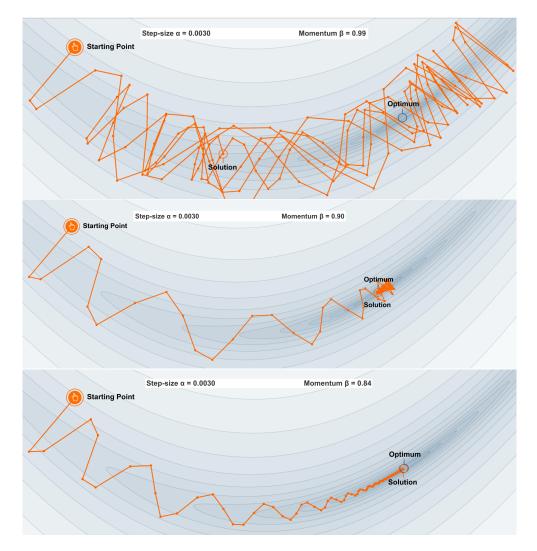

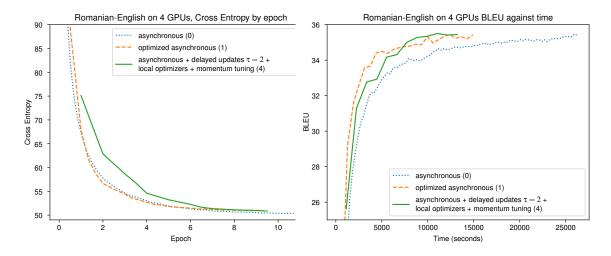

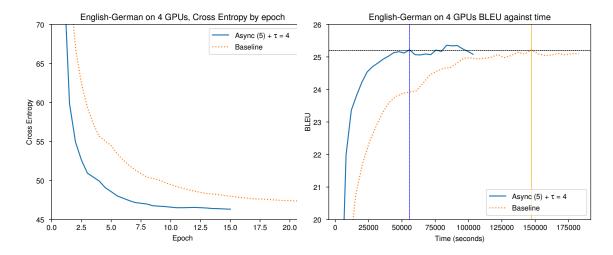

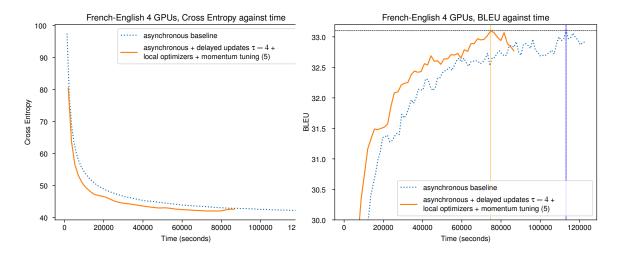

## N-gram language models for massively parallel devices